- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

Khắc mang wafer

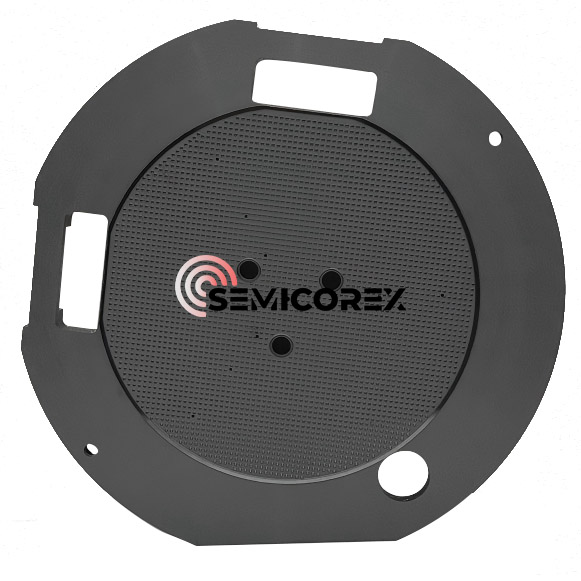

Semicorex Etching Wafer Carrier với lớp phủ CVD SIC là một giải pháp tiên tiến, hiệu suất cao phù hợp với các ứng dụng khắc bán dẫn đòi hỏi. Độ ổn định nhiệt vượt trội, sức cản hóa học và độ bền cơ học của nó làm cho nó trở thành một thành phần thiết yếu trong chế tạo wafer hiện đại, đảm bảo hiệu quả cao, độ tin cậy và hiệu quả chi phí cho các nhà sản xuất bán dẫn trên toàn thế giới.*

Gửi yêu cầu

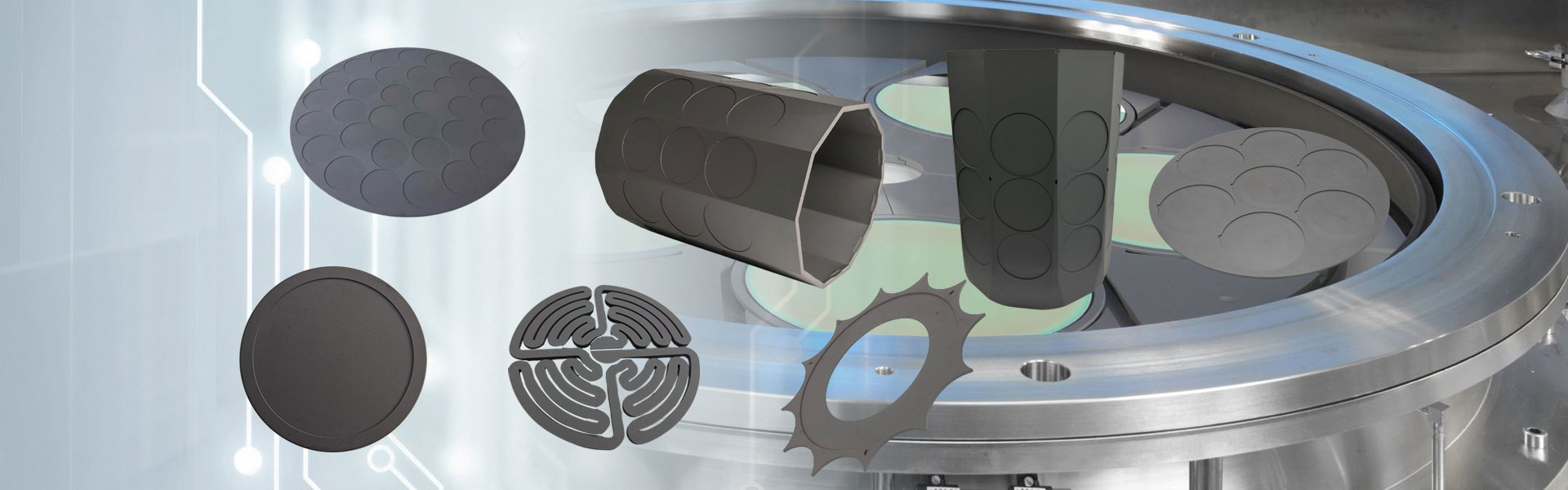

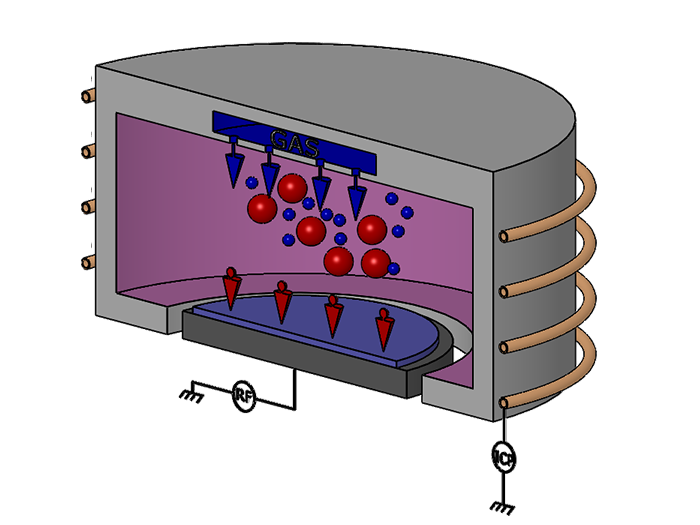

Semicorex Etching Wafer Carrier là một nền tảng hỗ trợ cơ chất hiệu suất cao được thiết kế cho các quy trình chế tạo chất bán dẫn, đặc biệt cho các ứng dụng khắc wafer. Được thiết kế với bazơ than chì tinh khiết cao và được phủ bằng lắng đọng hơi hóa học (CVD) cacbua silicon (SIC), chất mang wafer này cung cấp khả năng chống hóa học đặc biệt, độ ổn định nhiệt và độ bền cơ học, đảm bảo hiệu suất tối ưu trong môi trường khắc cao.

Các chất mang wafer khắc được phủ một lớp SIC CVD đồng nhất, giúp tăng cường đáng kể khả năng chống hóa học của nó chống lại huyết tương tích cực và khí ăn mòn được sử dụng trong quá trình khắc. CVD là công nghệ chính để chuẩn bị lớp phủ SIC trên bề mặt chất nền hiện nay. Quá trình chính là các nguyên liệu thô của chất phản ứng pha khí trải qua một loạt các phản ứng vật lý và hóa học trên bề mặt chất nền, và cuối cùng lắng đọng trên bề mặt chất nền để chuẩn bị lớp phủ SIC. Lớp phủ SIC được điều chế bởi công nghệ CVD được liên kết chặt chẽ với bề mặt chất nền, có thể cải thiện hiệu quả khả năng chống oxy hóa và khả năng chống cắt bỏ của vật liệu chất nền, nhưng thời gian lắng đọng của phương pháp này dài và khí phản ứng chứa một số khí độc hại.

Lớp phủ cacbua silicon CVDCác bộ phận được sử dụng rộng rãi trong thiết bị khắc, thiết bị MOCVD, thiết bị Epiticular SI và thiết bị epiticular SiC, thiết bị xử lý nhiệt nhanh và các trường khác. Nhìn chung, phân khúc thị trường lớn nhất của các bộ phận lớp phủ cacbua CVD Silicon là các thiết bị khắc và các bộ phận thiết bị epiticular. Do tính phản ứng và độ dẫn thấp của lớp phủ cacbua silicon CVD thành các loại khí khắc chứa clo và chứa flo, nó trở thành một vật liệu lý tưởng để tập trung các vòng và các bộ phận khác của thiết bị khắc plasma.Các bộ phận CVD sictrong các thiết bị khắc bao gồmTập trung nhẫn, Đầu vòi hoa sen, khay,Nhẫn cạnh, vv lấy vòng lấy nét làm ví dụ. Vòng lấy nét là một thành phần quan trọng được đặt bên ngoài wafer và tiếp xúc trực tiếp với wafer. Điện áp được áp dụng cho vòng để tập trung plasma đi qua vòng, do đó tập trung plasma vào wafer để cải thiện tính đồng nhất xử lý. Nhẫn lấy nét truyền thống được làm bằng silicon hoặc thạch anh. Với sự tiến bộ của thu nhỏ mạch tích hợp, nhu cầu và tầm quan trọng của các quá trình khắc trong sản xuất mạch tích hợp đang tăng lên, và sức mạnh và năng lượng của việc khắc plasma tiếp tục tăng.

Lớp phủ SIC cung cấp khả năng kháng vượt trội so với các hóa chất khắc trong huyết tương dựa trên fluorine (F₂) và clo (CL₂), ngăn ngừa sự thoái hóa và duy trì tính toàn vẹn cấu trúc so với sử dụng kéo dài. Sự mạnh mẽ hóa học này đảm bảo hiệu suất nhất quán và giảm rủi ro ô nhiễm trong quá trình xử lý wafer. Bộ vận chuyển wafer có thể được điều chỉnh theo các kích thước wafer khác nhau (ví dụ: 200mm, 300mm) và các yêu cầu hệ thống khắc cụ thể. Thiết kế khe tùy chỉnh và các mẫu lỗ có sẵn để tối ưu hóa định vị wafer, kiểm soát dòng khí và hiệu quả quy trình.

Ứng dụng và lợi ích

Chất mang wafer khắc chủ yếu được sử dụng trong sản xuất chất bán dẫn cho các quá trình khắc khô, bao gồm khắc huyết tương (PE), khắc ion phản ứng (RIE) và khắc ion phản ứng sâu (DRIE). Nó được áp dụng rộng rãi trong việc sản xuất các mạch tích hợp (ICS), các thiết bị MEMS, thiết bị điện tử và các tấm bán dẫn hợp chất. Lớp phủ SIC mạnh mẽ của nó đảm bảo kết quả khắc nhất quán bằng cách ngăn chặn sự xuống cấp vật liệu. Sự kết hợp giữa than chì và SIC cung cấp độ bền lâu dài, giảm chi phí bảo trì và thay thế. Bề mặt SIC mịn và dày đặc giảm thiểu việc tạo hạt, đảm bảo năng suất wafer cao và hiệu suất thiết bị vượt trội. Kháng đặc biệt với môi trường khắc khắc nghiệt làm giảm nhu cầu thay thế thường xuyên, cải thiện hiệu quả sản xuất.