- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

SiGe trong sản xuất chip: Báo cáo tin tức chuyên nghiệp

Sự phát triển của vật liệu bán dẫn

Trong lĩnh vực công nghệ bán dẫn hiện đại, nỗ lực không ngừng hướng tới việc thu nhỏ kích thước đã đẩy các giới hạn của vật liệu dựa trên silicon truyền thống. Để đáp ứng nhu cầu về hiệu suất cao và tiêu thụ điện năng thấp, SiGe (Silicon Germanium) đã nổi lên như một vật liệu tổng hợp được lựa chọn trong sản xuất chip bán dẫn nhờ các đặc tính vật lý và điện độc đáo của nó. Bài viết này đi sâu vàoquá trình epitaxycủa SiGe và vai trò của nó trong sự tăng trưởng epiticular, các ứng dụng silicon căng thẳng và cấu trúc Gate-All-Around (GAA).

Ý nghĩa của SiGe Epit Wax

1.1 Giới thiệu về Epitaxy trong sản xuất chip:

Epitaxy, thường được viết tắt là Epi, đề cập đến sự phát triển của một lớp tinh thể đơn trên chất nền đơn tinh thể có cùng cách sắp xếp mạng tinh thể. Lớp này có thể làđồng epiticular (chẳng hạn như Si/Si)hoặc dị epiticular (chẳng hạn như SiGe/Si hoặc SiC/Si). Các phương pháp khác nhau được sử dụng để tăng trưởng epiticular, bao gồm Epit Wax chùm phân tử (MBE), lắng đọng hơi hóa chất chân không cực cao (UHV/CVD), Epit Wax áp suất khí quyển và giảm áp (ATM & RP Epi). Bài viết này tập trung vào quá trình epit Wax của silicon (Si) và silicon-germanium (SiGe) được sử dụng rộng rãi trong sản xuất mạch tích hợp bán dẫn với silicon làm vật liệu nền.

1.2 Ưu điểm của SiGe Epitaxy:

Kết hợp một tỷ lệ nhất định germanium (Ge) trong quá trìnhquá trình epitaxytạo thành lớp đơn tinh thể SiGe không chỉ làm giảm độ rộng vùng cấm mà còn làm tăng tần số cắt của bóng bán dẫn (fT). Điều này làm cho nó có thể áp dụng rộng rãi trong các thiết bị tần số cao cho truyền thông không dây và quang học. Hơn nữa, trong các quy trình mạch tích hợp CMOS tiên tiến, sự không khớp mạng (khoảng 4%) giữa Ge và Si gây ra ứng suất mạng, tăng cường khả năng di động của các electron hoặc lỗ trống và do đó làm tăng dòng bão hòa và tốc độ phản hồi của thiết bị.

Quy trình xử lý Epit Wax SiGe toàn diện

2.1 Tiền xử lý:

Tấm silicon được xử lý trước dựa trên kết quả quy trình mong muốn, chủ yếu liên quan đến việc loại bỏ lớp oxit tự nhiên và tạp chất trên bề mặt tấm wafer. Đối với các tấm nền có chất nền bị pha tạp nhiều, điều quan trọng là phải xem xét liệu việc dán lại có cần thiết để giảm hiện tượng tự động pha tạp trong quá trình tiếp theo hay không.tăng trưởng epitaxy.

2.2 Khí tăng trưởng và điều kiện:

Khí silicon: Silane (SiH₄), Dichlorosilane (DCS, SiH₂Cl₂) và Trichlorosilane (TCS, SiHCl₃) là ba nguồn khí silicon được sử dụng phổ biến nhất. SiH₄ phù hợp cho các quy trình epit Wax hoàn toàn ở nhiệt độ thấp, trong khi TCS, được biết đến với tốc độ tăng trưởng nhanh, được sử dụng rộng rãi để chuẩn bị các vật liệu dàyepitaxy siliconcác lớp.

Khí Germanium: Germane (GeH₄) là nguồn chính để bổ sung germanium, được sử dụng cùng với các nguồn silicon để tạo thành hợp kim SiGe.

Epitaxy chọn lọc: Tăng trưởng có chọn lọc đạt được bằng cách điều chỉnh tỷ lệ tương đối củalắng đọng epitaxyvà khắc tại chỗ, sử dụng khí silicon chứa clo DCS. Tính chọn lọc là do sự hấp phụ của các nguyên tử Cl trên bề mặt silicon ít hơn so với trên oxit hoặc nitrit, tạo điều kiện cho sự phát triển của epiticular. SiH₄, thiếu nguyên tử Cl và có năng lượng kích hoạt thấp, thường chỉ được áp dụng cho các quá trình epit Wax hoàn toàn ở nhiệt độ thấp. Một nguồn silicon thường được sử dụng khác, TCS, có áp suất hơi thấp và ở dạng lỏng ở nhiệt độ phòng, cần tạo bọt H₂ để đưa nó vào buồng phản ứng. Tuy nhiên, nó tương đối rẻ tiền và thường được sử dụng vì tốc độ tăng trưởng nhanh (lên tới 5 μm/phút) để phát triển các lớp epit Wax silicon dày hơn, được ứng dụng rộng rãi trong sản xuất wafer epit Wafer silicon.

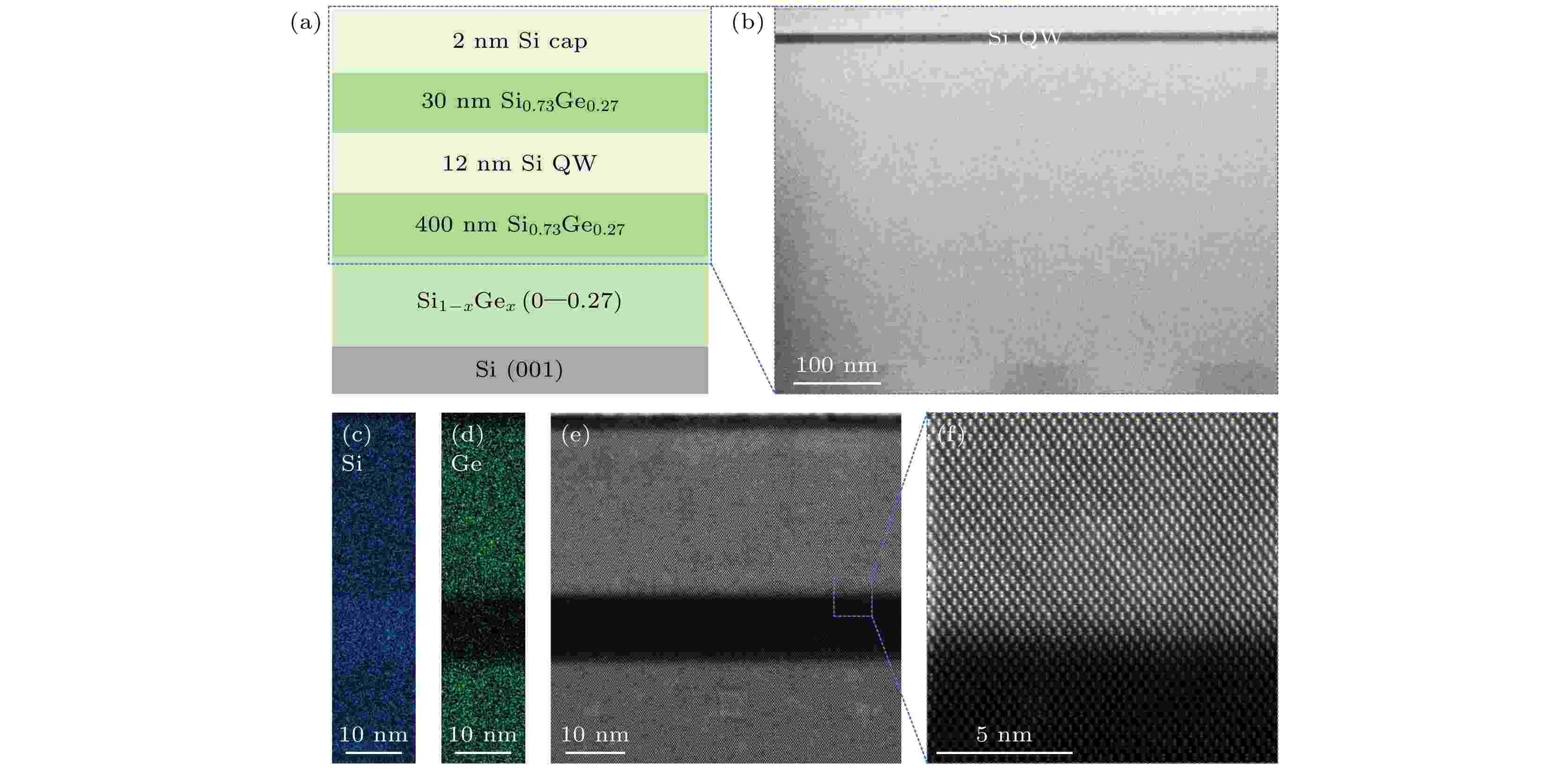

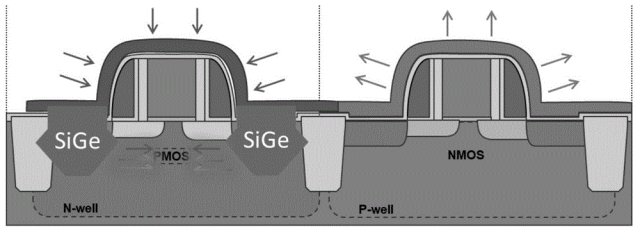

Silic căng trong lớp epitaxy

Trong lúctăng trưởng epiticular, Si đơn tinh thể epiticular được lắng đọng trên lớp SiGe thoải mái. Do sự không khớp mạng giữa Si và SiGe, lớp đơn tinh thể Si chịu ứng suất kéo từ lớp SiGe bên dưới, giúp tăng cường đáng kể độ linh động của điện tử trong bóng bán dẫn NMOS. Công nghệ này không chỉ làm tăng dòng bão hòa (Idsat) mà còn cải thiện tốc độ phản hồi của thiết bị. Đối với các thiết bị PMOS, các lớp SiGe được phát triển đồng trục ở vùng nguồn và vùng thoát sau khi ăn mòn để tạo ra ứng suất nén trên kênh, tăng cường khả năng di chuyển của lỗ và tăng dòng bão hòa.

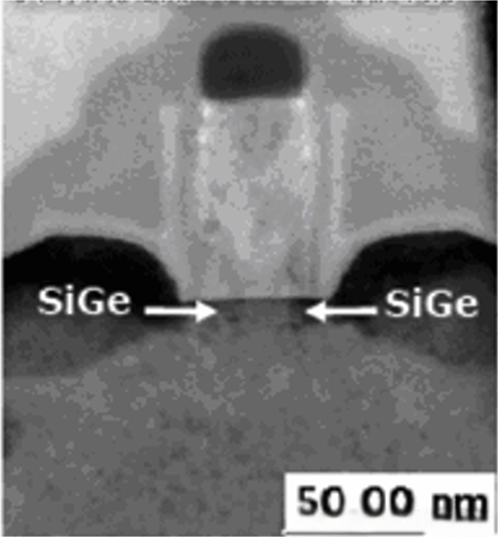

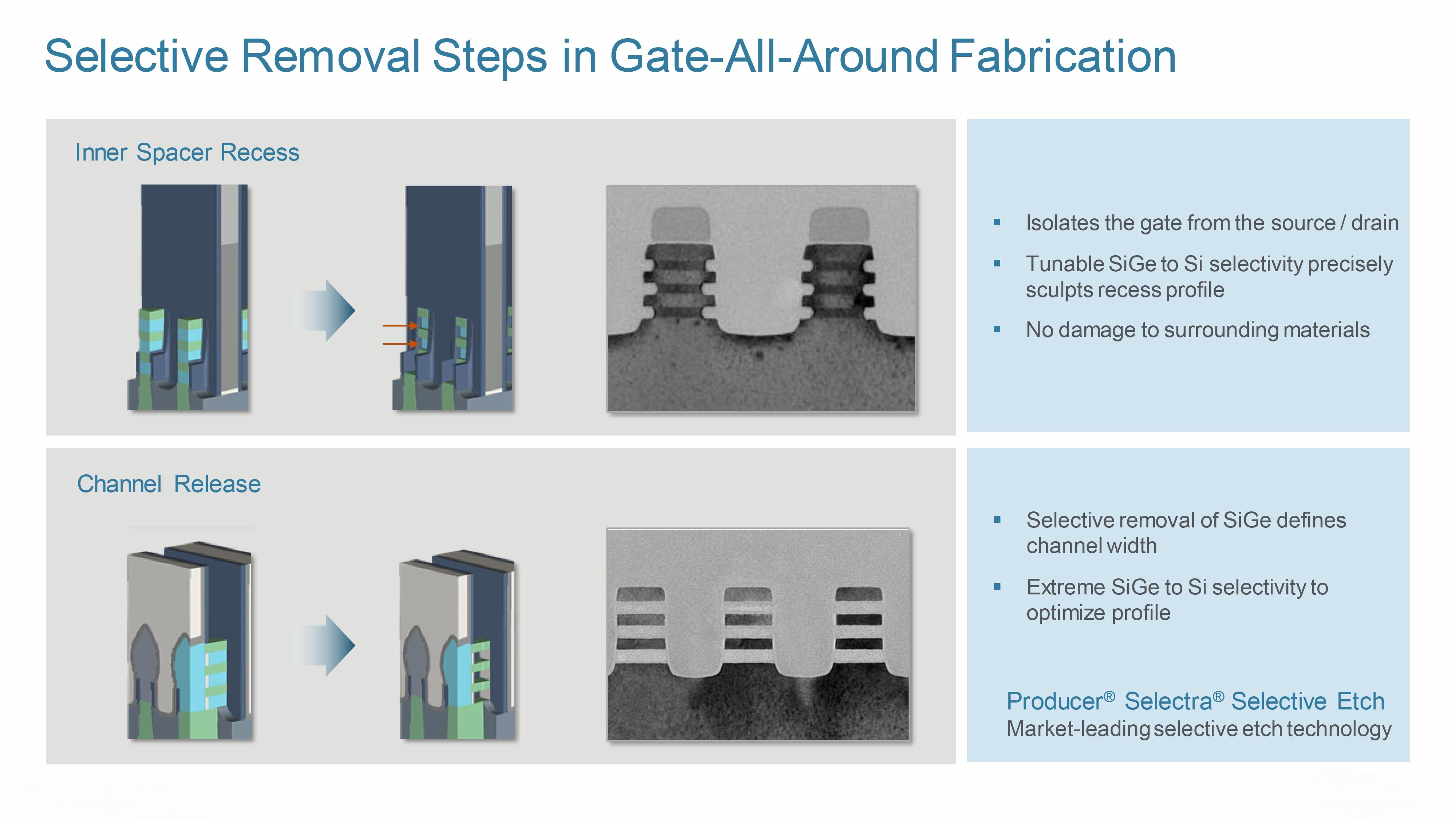

SiGe như một lớp hy sinh trong cấu trúc GAA

Trong quá trình sản xuất bóng bán dẫn dây nano Gate-All-Around (GAA), các lớp SiGe hoạt động như các lớp hy sinh. Các kỹ thuật ăn mòn dị hướng có độ chọn lọc cao, chẳng hạn như ăn mòn lớp bán nguyên tử (quasi-ALE), cho phép loại bỏ chính xác các lớp SiGe để tạo thành cấu trúc dây nano hoặc tấm nano.

Chúng tôi ở Semicorex chuyên vềGiải pháp than chì phủ SiC/TaCáp dụng trong tăng trưởng epiticular Si trong sản xuất chất bán dẫn, nếu bạn có bất kỳ thắc mắc hoặc cần thêm chi tiết, xin vui lòng liên hệ với chúng tôi.

Điện thoại liên hệ: +86-13567891907

Email: sales@semicorex.com