- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

Lớp epitaxy: Nền tảng của các thiết bị bán dẫn tiên tiến

Hình 1: Minh họa mối tương quan giữa nồng độ pha tạp, độ dày lớp và điện áp đánh thủng đối với các thiết bị đơn cực.

Việc chuẩn bị các lớp epiticular SiC chủ yếu bao gồm các kỹ thuật như Tăng trưởng bay hơi, Epit Wax pha lỏng (LPE), Epit Wax chùm phân tử (MBE) và lắng đọng hơi hóa học (CVD), trong đó CVD là phương pháp chủ yếu để sản xuất hàng loạt trong các nhà máy.

Bảng 1: Cung cấp cái nhìn tổng quan so sánh về các phương pháp chuẩn bị lớp epitaxy chính.

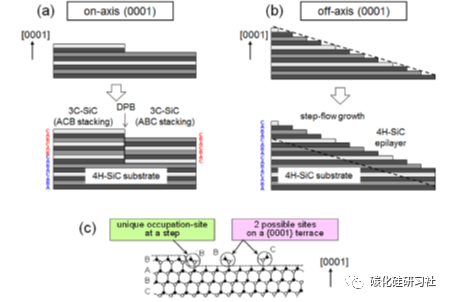

Một cách tiếp cận mang tính đột phá liên quan đến sự phát triển trên các chất nền {0001} ngoài trục ở một góc nghiêng cụ thể, như được mô tả trong Hình 2(b). Phương pháp này làm tăng đáng kể mật độ bước trong khi giảm kích thước bước, tạo điều kiện thuận lợi cho quá trình tạo mầm chủ yếu tại các vị trí nhóm bước và do đó, cho phép lớp epiticular tái tạo hoàn hảo trình tự xếp chồng của chất nền, loại bỏ sự cùng tồn tại của nhiều kiểu.

Hình 2: Minh họa quy trình vật lý của quá trình epitaxy được kiểm soát theo bước trong 4H-SiC.

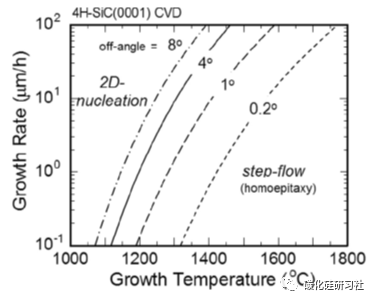

Hình 3: Hiển thị các điều kiện quan trọng cho sự phát triển CVD trong quá trình epitaxy được kiểm soát theo bước đối với 4H-SiC.

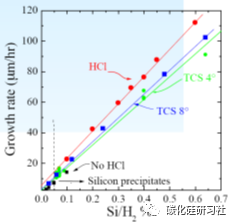

Hình 4: So sánh tốc độ tăng trưởng dưới các nguồn silicon khác nhau đối với epit Wax 4H-SiC.

Trong lĩnh vực ứng dụng điện áp thấp và trung bình (ví dụ: thiết bị 1200V), công nghệ epit Wax SiC đã đạt đến giai đoạn trưởng thành, mang lại độ đồng đều tương đối vượt trội về độ dày, nồng độ pha tạp và phân bố khuyết tật, đáp ứng đầy đủ các yêu cầu cho SBD điện áp thấp và trung áp , MOS, thiết bị JBS và các thiết bị khác.

Tuy nhiên, lĩnh vực điện áp cao vẫn còn nhiều thách thức. Ví dụ, các thiết bị có điện áp định mức 10000V yêu cầu các lớp epiticular dày khoảng 100μm, nhưng các lớp này có độ dày và độ đồng đều pha tạp kém hơn đáng kể so với các thiết bị có điện áp thấp tương tự, chưa kể đến tác động bất lợi của các khuyết tật hình tam giác đến hiệu suất tổng thể của thiết bị. Các ứng dụng điện áp cao, có xu hướng ưu tiên các thiết bị lưỡng cực, cũng đặt ra yêu cầu nghiêm ngặt về tuổi thọ của sóng mang thiểu số, đòi hỏi phải tối ưu hóa quy trình để nâng cao thông số này.

Hiện nay, thị trường đang bị thống trị bởi các tấm wafer epiticular SiC 4 inch và 6 inch, với tỷ lệ các tấm wafer epiticular SiC đường kính lớn tăng dần. Kích thước của tấm wafer epiticular SiC về cơ bản được xác định bởi kích thước của chất nền SiC. Với chất nền SiC 6 inch hiện đã có sẵn trên thị trường, quá trình chuyển đổi từ epit Wax SiC 4 inch sang 6 inch đang được tiến hành đều đặn.

Khi công nghệ chế tạo chất nền SiC tiến bộ và năng lực sản xuất mở rộng, giá thành của chất nền SiC ngày càng giảm. Do chất nền chiếm hơn 50% chi phí của tấm wafer epiticular, nên giá chất nền giảm dự kiến sẽ dẫn đến chi phí cho epit Wax SiC thấp hơn, từ đó hứa hẹn một tương lai tươi sáng hơn cho ngành.**