- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

Xử lý chất nền đơn tinh thể SiC

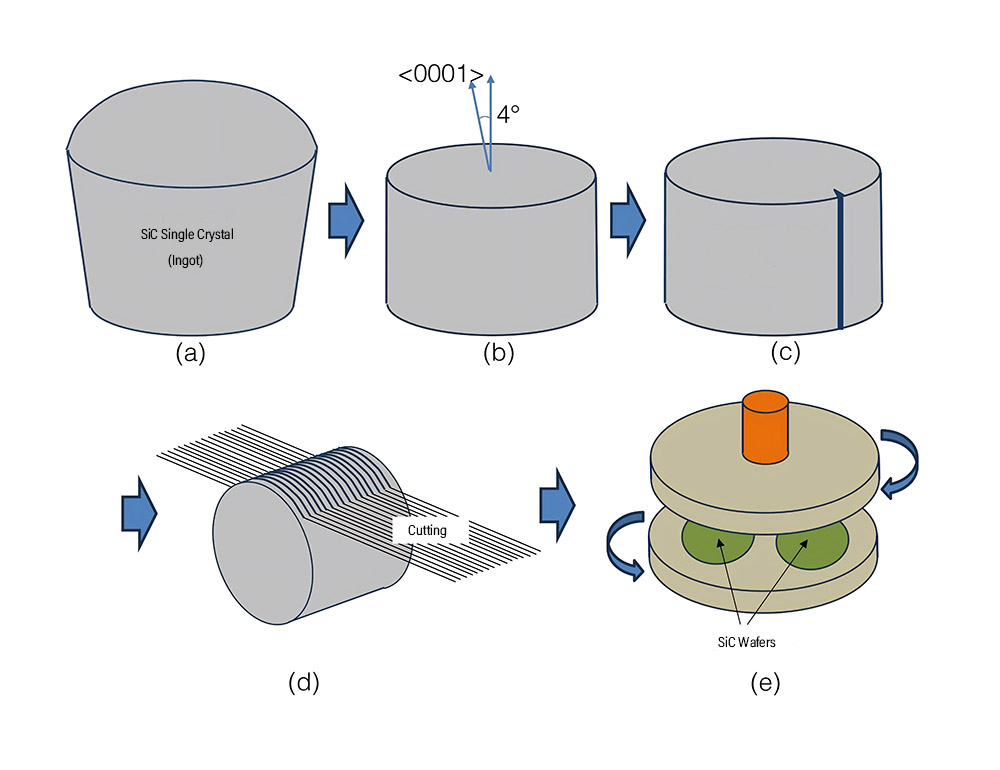

Tinh thể đơn silic cacbua (SiC)chủ yếu được sản xuất bằng phương pháp thăng hoa. Sau khi lấy tinh thể ra khỏi nồi nấu kim loại, cần phải thực hiện một số bước xử lý phức tạp để tạo ra các tấm bán dẫn có thể sử dụng được. Bước đầu tiên là xác định hướng tinh thể của bó SiC. Sau đó, bó hoa trải qua quá trình mài đường kính ngoài để đạt được hình trụ. Đối với các tấm SiC loại n, thường được sử dụng trong các thiết bị điện, cả bề mặt trên và dưới của tinh thể hình trụ thường được gia công để tạo ra một mặt phẳng ở góc 4° so với mặt {0001}.

Tiếp theo, quá trình xử lý tiếp tục với việc cắt cạnh định hướng hoặc cắt khía để xác định hướng tinh thể của bề mặt wafer. Trong sản xuất đường kính lớntấm wafer SiC, khía hình định hướng là một kỹ thuật phổ biến. Tinh thể đơn SiC hình trụ sau đó được cắt thành các tấm mỏng, chủ yếu sử dụng kỹ thuật cắt nhiều dây. Quá trình này liên quan đến việc đặt chất mài mòn giữa dây cắt và tinh thể SiC đồng thời tạo áp lực để tạo điều kiện thuận lợi cho chuyển động cắt.

Hình 1 Tổng quan về công nghệ xử lý tấm wafer SiC

(a) Loại bỏ phôi SiC khỏi nồi nấu kim loại; (b) Mài hình trụ; (c) Cắt cạnh hoặc cắt theo hướng; (d) Cắt nhiều dây; (e) Mài và đánh bóng

Sau khi cắt lát,tấm wafer SiCthường thể hiện sự không nhất quán về độ dày và bề mặt không đồng đều, đòi hỏi phải xử lý làm phẳng thêm. Điều này bắt đầu bằng việc mài để loại bỏ sự không đồng đều trên bề mặt ở cấp độ micron. Trong giai đoạn này, hoạt động mài mòn có thể gây ra các vết xước nhỏ và các khuyết điểm trên bề mặt. Vì vậy, bước đánh bóng tiếp theo là rất quan trọng để đạt được độ hoàn thiện giống như gương. Không giống như mài, đánh bóng sử dụng chất mài mòn mịn hơn và cần được chăm sóc tỉ mỉ để tránh trầy xước hoặc hư hỏng bên trong, đảm bảo độ mịn bề mặt cao.

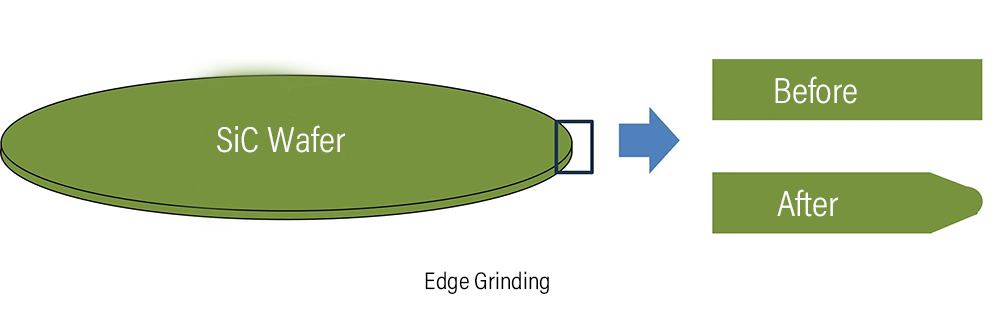

Thông qua các thủ tục này,tấm wafer SiCphát triển từ xử lý thô đến gia công chính xác, cuối cùng tạo ra bề mặt phẳng, giống như gương phù hợp với các thiết bị hiệu suất cao. Tuy nhiên, việc giải quyết các cạnh sắc thường hình thành xung quanh chu vi của tấm wafer được đánh bóng là điều cần thiết. Các cạnh sắc này rất dễ bị gãy khi tiếp xúc với các vật khác. Để giảm thiểu sự dễ vỡ này, việc mài cạnh của chu vi tấm bán dẫn là cần thiết. Các tiêu chuẩn công nghiệp đã được thiết lập để đảm bảo độ tin cậy và an toàn của tấm bán dẫn trong quá trình sử dụng tiếp theo.

Độ cứng vượt trội của SiC khiến nó trở thành vật liệu mài mòn lý tưởng trong các ứng dụng gia công khác nhau. Tuy nhiên, điều này cũng đặt ra những thách thức trong việc xử lý các khối SiC thành các tấm bán dẫn vì đây là một quá trình phức tạp và tốn thời gian và liên tục được tối ưu hóa. Một cải tiến đầy hứa hẹn để cải thiện các phương pháp cắt lát truyền thống là công nghệ cắt laser. Trong kỹ thuật này, một chùm tia laser được hướng từ đỉnh tinh thể SiC hình trụ, tập trung ở độ sâu cắt mong muốn để tạo ra một vùng sửa đổi bên trong tinh thể. Bằng cách quét toàn bộ bề mặt, vùng sửa đổi này dần dần mở rộng thành một mặt phẳng, cho phép tách các tấm mỏng. So với việc cắt nhiều dây thông thường, thường gây ra tổn thất đường cắt đáng kể và có thể gây ra các bất thường trên bề mặt, việc cắt lát bằng laser làm giảm đáng kể tổn thất đường cắt và thời gian xử lý, định vị nó là một phương pháp đầy hứa hẹn cho sự phát triển trong tương lai.

Một công nghệ cắt cải tiến khác là ứng dụng cắt phóng điện, tạo ra sự phóng điện giữa dây kim loại và tinh thể SiC. Phương pháp này có ưu điểm là giảm tổn thất đường cắt đồng thời nâng cao hơn nữa hiệu quả xử lý.

Một cách tiếp cận đặc biệt đểtấm wafer SiCsản xuất bao gồm việc gắn một màng mỏng đơn tinh thể SiC vào một chất nền không đồng nhất, từ đó chế tạotấm wafer SiC. Quá trình liên kết và tách rời này bắt đầu bằng việc bơm các ion hydro vào tinh thể đơn SiC đến độ sâu xác định trước. Tinh thể SiC, hiện được trang bị một lớp cấy ion, được xếp lớp trên một chất nền hỗ trợ mịn, chẳng hạn như SiC đa tinh thể. Bằng cách tạo áp suất và nhiệt, lớp tinh thể đơn SiC được chuyển lên đế đỡ, hoàn thành việc tách rời. Lớp SiC được chuyển trải qua quá trình xử lý làm phẳng bề mặt và có thể được tái sử dụng trong quá trình liên kết. Mặc dù giá thành của chất nền hỗ trợ thấp hơn so với tinh thể đơn SiC nhưng vẫn còn những thách thức kỹ thuật. Tuy nhiên, nghiên cứu và phát triển trong lĩnh vực này tiếp tục tiến triển tích cực nhằm giảm chi phí sản xuất chung củatấm wafer SiC.

Tóm lại, quá trình xử lýChất nền đơn tinh thể SiCbao gồm nhiều giai đoạn, từ mài và cắt đến đánh bóng và xử lý cạnh. Những cải tiến như cắt laser và gia công bằng phóng điện đang nâng cao hiệu quả và giảm lãng phí vật liệu, trong khi các phương pháp liên kết chất nền mới đưa ra các giải pháp thay thế để sản xuất tấm bán dẫn hiệu quả về mặt chi phí. Khi ngành tiếp tục phấn đấu cải tiến kỹ thuật và tiêu chuẩn, mục tiêu cuối cùng vẫn là sản xuất chất lượng caotấm wafer SiCđáp ứng nhu cầu của các thiết bị điện tử tiên tiến.