- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

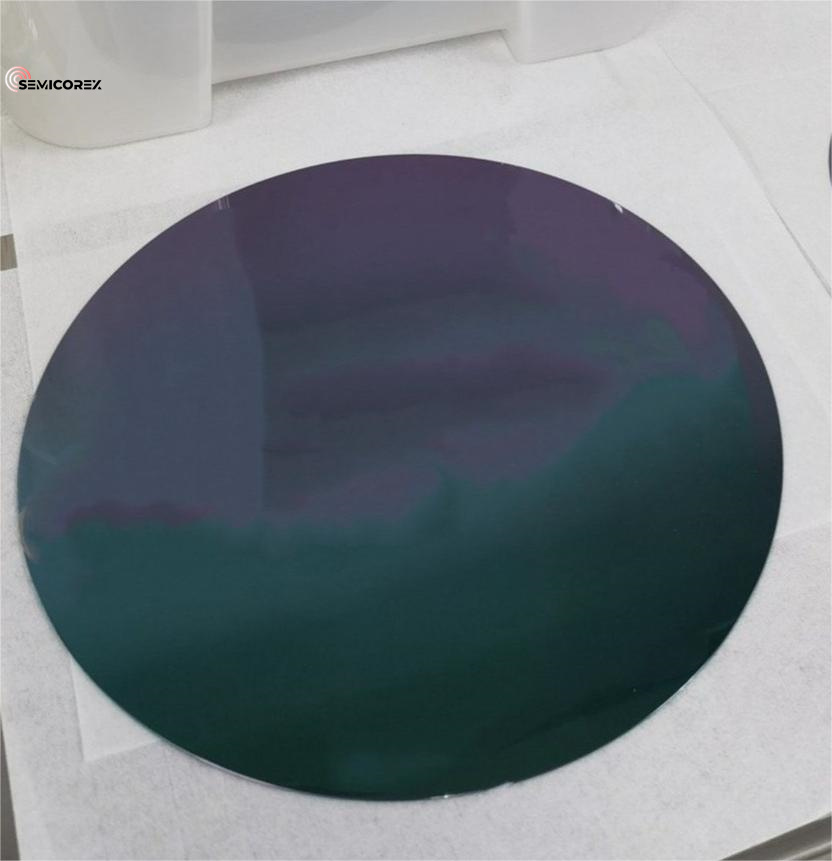

Bánh xốp silicon

Vật liệu silicon là vật liệu rắn có tính chất điện bán dẫn và độ ổn định vật lý nhất định, đồng thời cung cấp chất nền hỗ trợ cho quy trình sản xuất mạch tích hợp tiếp theo. Nó là vật liệu chính cho các mạch tích hợp dựa trên silicon. Hơn 95% thiết bị bán dẫn và hơn 90% mạch tích hợp trên thế giới được chế tạo trên tấm silicon.

Theo các phương pháp tăng trưởng tinh thể đơn khác nhau, các tinh thể đơn silicon được chia thành hai loại: Czochralski (CZ) và vùng nổi (FZ). Tấm silicon có thể được chia đại khái thành ba loại: tấm được đánh bóng, tấm wafer epiticular và tấm cách điện Silicon (SOI).

Tấm wafer đánh bóng silicon đề cập đến mộttấm siliconđược hình thành bằng cách đánh bóng bề mặt. Nó là một tấm wafer tròn có độ dày dưới 1mm được xử lý bằng cách cắt, mài, đánh bóng, làm sạch và các quy trình khác của một thanh tinh thể đơn. Nó chủ yếu được sử dụng trong các mạch tích hợp và thiết bị rời rạc và chiếm một vị trí quan trọng trong chuỗi công nghiệp bán dẫn.

Khi các nguyên tố nhóm V như phốt pho, antimon, asen, v.v. được pha tạp vào các tinh thể đơn silicon, vật liệu dẫn điện loại N sẽ được hình thành; khi các nguyên tố nhóm III như boron được pha tạp vào silicon sẽ tạo thành vật liệu dẫn điện loại P. Điện trở suất của các tinh thể đơn silicon được xác định bởi lượng nguyên tố pha tạp được pha tạp. Lượng pha tạp càng lớn thì điện trở suất càng thấp. Tấm đánh bóng silicon pha tạp nhẹ thường dùng để chỉ tấm đánh bóng silicon có điện trở suất lớn hơn 0,1W·cm, được sử dụng rộng rãi trong sản xuất mạch tích hợp và bộ nhớ quy mô lớn; Tấm đánh bóng silicon pha tạp nặng thường dùng để chỉ tấm đánh bóng silicon có điện trở suất nhỏ hơn 0,1W·cm, thường được sử dụng làm vật liệu nền cho tấm silicon epiticular và được sử dụng rộng rãi trong sản xuất thiết bị điện bán dẫn.

Tấm đánh bóng silicontạo thành một vùng sạch trên bề mặttấm siliconsau khi ủ nhiệt được gọi là tấm ủ silicon. Những loại thường được sử dụng là tấm ủ hydro và tấm ủ argon. Tấm silicon 300mm và một số tấm silicon 200mm có yêu cầu cao hơn đòi hỏi phải sử dụng quy trình đánh bóng hai mặt. Do đó, công nghệ thu nhận bên ngoài đưa trung tâm thu nhận thông qua mặt sau của tấm wafer silicon rất khó áp dụng. Quy trình gettering bên trong sử dụng quy trình ủ để hình thành trung tâm gettering bên trong đã trở thành quy trình gettering chủ đạo cho các tấm silicon kích thước lớn. So với các tấm wafer được đánh bóng thông thường, các tấm wafer được ủ có thể cải thiện hiệu suất thiết bị và tăng năng suất, được sử dụng rộng rãi trong sản xuất mạch tích hợp kỹ thuật số và analog và chip bộ nhớ.

Nguyên tắc cơ bản của sự phát triển tinh thể đơn tan chảy theo vùng là dựa vào sức căng bề mặt của chất tan chảy để treo vùng nóng chảy giữa thanh silicon đa tinh thể và tinh thể đơn phát triển bên dưới, đồng thời tinh chế và phát triển các tinh thể đơn silicon bằng cách di chuyển vùng nóng chảy lên trên. Các tinh thể đơn silicon nóng chảy vùng không bị ô nhiễm bởi nồi nấu kim loại và có độ tinh khiết cao. Chúng thích hợp để sản xuất các tinh thể đơn silicon loại N (bao gồm cả các tinh thể đơn pha tạp neutron biến đổi neutron) có điện trở suất cao hơn 200Ω·cm và các tinh thể đơn silicon loại P có điện trở suất cao. Các tinh thể đơn silicon nóng chảy vùng chủ yếu được sử dụng trong sản xuất các thiết bị điện áp cao và công suất cao.

Tấm wafer silicondùng để chỉ một vật liệu trên đó một hoặc nhiều lớp màng mỏng đơn tinh thể silicon được phát triển bằng cách lắng đọng epiticular pha hơi trên đế và chủ yếu được sử dụng để sản xuất các mạch tích hợp và thiết bị rời rạc khác nhau.

Trong các quy trình mạch tích hợp CMOS tiên tiến, để cải thiện tính toàn vẹn của lớp oxit cổng, cải thiện sự rò rỉ trong kênh và nâng cao độ tin cậy của mạch tích hợp, các tấm wafer silicon thường được sử dụng, nghĩa là một lớp màng mỏng silicon được epiticular đồng nhất được phát triển trên một tấm wafer được đánh bóng bằng silicon pha tạp nhẹ, có thể tránh được những thiếu sót về hàm lượng oxy cao và nhiều khuyết tật trên bề mặt của tấm wafer được đánh bóng bằng silicon nói chung; trong khi đối với các tấm epiticular silicon được sử dụng cho các mạch tích hợp nguồn và các thiết bị rời rạc, một lớp lớp epiticular có điện trở suất cao thường được trồng trên chất nền silicon có điện trở suất thấp (wafer silicon được đánh bóng pha tạp nặng). Trong môi trường ứng dụng công suất cao và điện áp cao, điện trở suất thấp của chất nền silicon có thể làm giảm điện trở bật và lớp epiticular có điện trở suất cao có thể làm tăng điện áp đánh thủng của thiết bị.

SOI (Chất cách điện silicon)là silicon trên một lớp cách điện. Đó là một cấu trúc "bánh sandwich" với lớp silicon trên cùng (Top Silicon), lớp chôn silicon dioxide ở giữa (HỘP) và lớp nền silicon hỗ trợ (Tay cầm) bên dưới. Là vật liệu nền mới cho sản xuất mạch tích hợp, ưu điểm chính của SOI là nó có thể đạt được khả năng cách điện cao thông qua lớp oxit, điều này sẽ làm giảm hiệu quả điện dung ký sinh và rò rỉ của các tấm silicon, điều này có lợi cho việc sản xuất các tấm silicon cao cấp mạch tích hợp quy mô cực lớn tốc độ, công suất thấp, tích hợp cao và độ tin cậy cao và được sử dụng rộng rãi trong các thiết bị điện cao áp, thiết bị thụ động quang học, MEMS và các lĩnh vực khác. Hiện nay, công nghệ điều chế vật liệu SOI chủ yếu bao gồm công nghệ liên kết (BESOI), công nghệ tước thông minh (Smart-Cut), công nghệ cấy ion oxy (SIMOX), công nghệ liên kết phun oxy (Simbond), v.v. Công nghệ chủ đạo nhất là thông minh. công nghệ tước.

tấm silicon SOIcó thể được chia thành các tấm silicon SOI màng mỏng và tấm silicon SOI màng dày. Độ dày của lớp silicon trên cùng của màng mỏngtấm silicon SOInhỏ hơn 1um. Hiện tại, 95% thị trường wafer silicon SOI màng mỏng tập trung ở kích thước 200mm và 300mm, và động lực thị trường của nó chủ yếu đến từ các sản phẩm tốc độ cao, năng lượng thấp, đặc biệt là trong các ứng dụng bộ vi xử lý. Ví dụ, trong các quy trình nâng cao dưới 28nm, silicon đã cạn kiệt hoàn toàn trên chất cách điện (FD-SOI) có những ưu điểm về hiệu suất rõ ràng là tiêu thụ điện năng thấp, bảo vệ bức xạ và chịu nhiệt độ cao. Đồng thời, việc sử dụng các giải pháp SOI có thể làm giảm đáng kể quá trình sản xuất. Độ dày silicon trên cùng của tấm silicon SOI màng dày lớn hơn 1um và độ dày lớp chôn là 0,5-4um. Nó chủ yếu được sử dụng trong các thiết bị điện và lĩnh vực MEMS, đặc biệt là trong điều khiển công nghiệp, điện tử ô tô, thông tin liên lạc không dây, v.v. và thường sử dụng các sản phẩm có đường kính 150mm và 200mm.