- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

Vai trò quan trọng của chất nền SiC và sự phát triển tinh thể trong ngành bán dẫn

Trong chuỗi công nghiệp cacbua silic (SiC), các nhà cung cấp chất nền nắm giữ đòn bẩy đáng kể, chủ yếu là do sự phân bổ giá trị.Chất nền SiC chiếm 47% tổng giá trị, tiếp theo là lớp epiticular với 23%, trong khi thiết kế và sản xuất thiết bị chiếm 30% còn lại. Chuỗi giá trị đảo ngược này bắt nguồn từ những rào cản công nghệ cao vốn có đối với việc sản xuất lớp nền và lớp epiticular.

3 thách thức lớn cản trở sự phát triển của chất nền SiC:điều kiện tăng trưởng nghiêm ngặt, tốc độ tăng trưởng chậm và yêu cầu khắt khe về tinh thể học. Những sự phức tạp này góp phần làm tăng độ khó xử lý, cuối cùng dẫn đến năng suất sản phẩm thấp và chi phí cao. Hơn nữa, độ dày và nồng độ pha tạp của lớp epiticular là những thông số quan trọng ảnh hưởng trực tiếp đến hiệu suất thiết bị cuối cùng.

Quy trình sản xuất chất nền SiC:

Tổng hợp nguyên liệu thô:Bột silicon và carbon có độ tinh khiết cao được trộn tỉ mỉ theo một công thức cụ thể. Hỗn hợp này trải qua phản ứng ở nhiệt độ cao (trên 2000°C) để tổng hợp các hạt SiC có cấu trúc tinh thể và kích thước hạt được kiểm soát. Quá trình nghiền, sàng và làm sạch tiếp theo mang lại bột SiC có độ tinh khiết cao thích hợp cho sự phát triển của tinh thể.

Tăng trưởng tinh thể:Là bước quan trọng nhất trong quá trình sản xuất chất nền SiC, sự phát triển tinh thể quyết định tính chất điện của chất nền. Hiện nay, phương pháp Vận chuyển hơi vật lý (PVT) đang chiếm ưu thế trong sự phát triển tinh thể SiC thương mại. Các lựa chọn thay thế bao gồm Lắng đọng hơi hóa học ở nhiệt độ cao (HT-CVD) và Epit Wax pha lỏng (LPE), mặc dù việc áp dụng thương mại của chúng vẫn còn hạn chế.

Chế biến tinh thể:Giai đoạn này bao gồm việc biến các khối SiC thành các tấm wafer được đánh bóng thông qua một loạt các bước tỉ mỉ: xử lý phôi, cắt lát wafer, mài, đánh bóng và làm sạch. Mỗi bước đều yêu cầu thiết bị có độ chính xác cao và chuyên môn cao, cuối cùng là đảm bảo chất lượng và hiệu suất của chất nền SiC cuối cùng.

1. Những thách thức kỹ thuật trong tăng trưởng tinh thể SiC:

Sự tăng trưởng của tinh thể SiC phải đối mặt với một số rào cản kỹ thuật:

Nhiệt độ tăng trưởng cao:Vượt quá 2300°C, những nhiệt độ này đòi hỏi phải kiểm soát chặt chẽ cả nhiệt độ và áp suất trong lò tăng trưởng.

Kiểm soát đa hình:SiC có hơn 250 polytype, trong đó 4H-SiC là loại được ưa chuộng nhất cho các ứng dụng điện tử. Để đạt được polytype cụ thể này đòi hỏi phải kiểm soát chính xác tỷ lệ silicon-carbon, độ dốc nhiệt độ và động lực dòng khí trong quá trình tăng trưởng.

Tốc độ tăng trưởng chậm:PVT tuy được thành lập về mặt thương mại nhưng có tốc độ tăng trưởng chậm khoảng 0,3-0,5mm/h. Việc phát triển một tinh thể 2cm mất khoảng 7 ngày, với chiều dài tinh thể tối đa có thể đạt được giới hạn ở mức 3-5cm. Điều này hoàn toàn trái ngược với sự phát triển của tinh thể silicon, nơi các bó hoa đạt chiều cao 2-3m trong vòng 72 giờ, với đường kính đạt 6-8 inch và thậm chí 12 inch ở các cơ sở mới. Sự khác biệt này giới hạn đường kính phôi SiC, thường dao động từ 4 đến 6 inch.

Trong khi Vận chuyển hơi vật lý (PVT) chi phối sự phát triển tinh thể SiC thương mại, các phương pháp thay thế như lắng đọng hơi hóa học ở nhiệt độ cao (HT-CVD) và Epit Wax pha lỏng (LPE) mang lại những lợi thế khác biệt. Tuy nhiên, việc khắc phục những hạn chế của chúng và nâng cao tốc độ tăng trưởng cũng như chất lượng tinh thể là rất quan trọng để áp dụng rộng rãi hơn cho ngành SiC.

Dưới đây là tổng quan so sánh về các kỹ thuật phát triển tinh thể này:

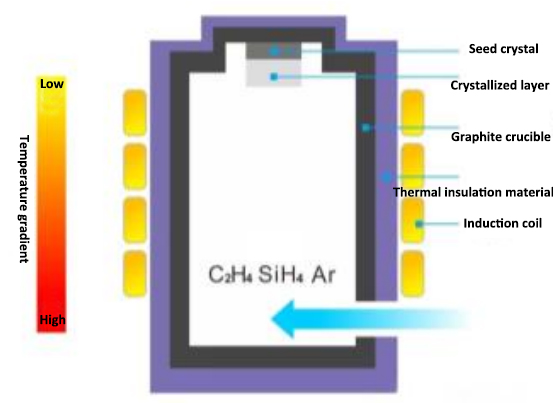

(1) Vận chuyển hơi vật lý (PVT):

Nguyên tắc: Sử dụng cơ chế “thăng hoa-vận chuyển-tái kết tinh” để phát triển tinh thể SiC.

Quy trình: Bột carbon và silicon có độ tinh khiết cao được trộn theo tỷ lệ chính xác. Bột SiC và tinh thể hạt tương ứng được đặt ở đáy và trên cùng của nồi nấu kim loại trong lò tăng trưởng. Nhiệt độ vượt quá 2000°C tạo ra một gradient nhiệt độ, làm cho bột SiC thăng hoa và kết tinh lại trên tinh thể hạt, tạo thành bó hoa.

Nhược điểm: Tốc độ tăng trưởng chậm (khoảng 2cm trong 7 ngày), dễ bị phản ứng ký sinh dẫn đến mật độ khuyết tật cao hơn trong tinh thể phát triển.

(2) Lắng đọng hơi hóa học ở nhiệt độ cao (HT-CVD):

Nguyên tắc: Ở nhiệt độ từ 2000-2500°C, các khí tiền chất có độ tinh khiết cao như silan, etan hoặc propan và hydro được đưa vào buồng phản ứng. Những khí này phân hủy ở vùng nhiệt độ cao, tạo thành tiền chất SiC dạng khí, sau đó lắng đọng và kết tinh thành tinh thể mầm ở vùng nhiệt độ thấp hơn.

Ưu điểm: Cho phép tinh thể phát triển liên tục, sử dụng tiền chất khí có độ tinh khiết cao tạo ra tinh thể SiC có độ tinh khiết cao hơn và ít khuyết tật hơn.

Nhược điểm: Tốc độ tăng trưởng chậm (khoảng 0,4-0,5mm/h), chi phí thiết bị và vận hành cao, dễ bị tắc nghẽn các đầu vào và đầu ra khí.

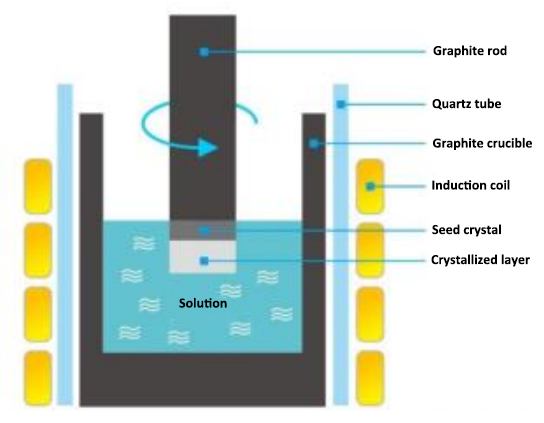

(3) Epitaxy pha lỏng (LPE):

(Mặc dù không có trong đoạn trích của bạn, nhưng tôi đang bổ sung thêm thông tin tổng quan ngắn gọn về LPE cho đầy đủ.)

Nguyên tắc: Sử dụng cơ chế “hòa tan-kết tủa”. Ở nhiệt độ từ 1400-1800°C, carbon được hòa tan trong silicon nóng chảy có độ tinh khiết cao. Tinh thể SiC kết tủa ra khỏi dung dịch siêu bão hòa khi nó nguội đi.

Ưu điểm: Nhiệt độ tăng trưởng thấp hơn làm giảm ứng suất nhiệt trong quá trình làm mát, dẫn đến mật độ khuyết tật thấp hơn và chất lượng tinh thể cao hơn. Cung cấp tốc độ tăng trưởng nhanh hơn đáng kể so với PVT.

Nhược điểm: Dễ bị nhiễm bẩn kim loại từ nồi nấu kim loại, bị giới hạn về kích thước tinh thể có thể đạt được, chủ yếu chỉ giới hạn ở quy mô phòng thí nghiệm.

Mỗi phương pháp đều có những ưu điểm và hạn chế riêng. Việc lựa chọn kỹ thuật tăng trưởng tối ưu phụ thuộc vào yêu cầu ứng dụng cụ thể, cân nhắc về chi phí và đặc tính tinh thể mong muốn.

2. Những thách thức và giải pháp xử lý tinh thể SiC:

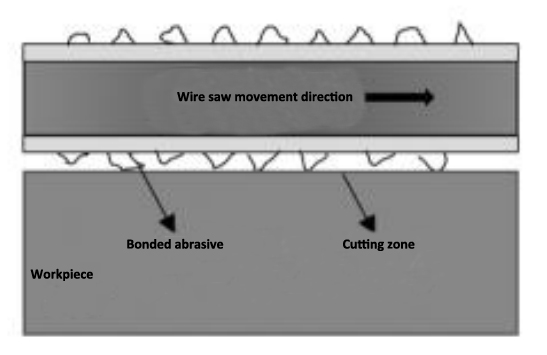

Cắt lát wafer:Độ cứng, độ giòn và khả năng chống mài mòn của SiC khiến việc cắt lát trở nên khó khăn. Việc cưa dây kim cương truyền thống rất tốn thời gian, lãng phí và tốn kém. Các giải pháp bao gồm kỹ thuật cắt hạt bằng laser và tách nguội để cải thiện hiệu quả cắt lát và năng suất wafer.

Làm mỏng wafer:Độ bền đứt gãy thấp của SiC khiến nó dễ bị nứt trong quá trình làm mỏng, cản trở việc giảm độ dày đồng đều. Các kỹ thuật hiện tại dựa vào mài quay, khiến bánh xe bị mài mòn và hư hỏng bề mặt. Các phương pháp tiên tiến như mài có hỗ trợ rung siêu âm và đánh bóng cơ học điện hóa đang được khám phá để nâng cao tốc độ loại bỏ vật liệu và giảm thiểu khuyết tật bề mặt.

3. Triển vọng tương lai:

Tối ưu hóa sự phát triển tinh thể SiC và xử lý wafer là rất quan trọng để áp dụng SiC rộng rãi. Nghiên cứu trong tương lai sẽ tập trung vào việc tăng tốc độ tăng trưởng, cải thiện chất lượng tinh thể và nâng cao hiệu quả xử lý tấm bán dẫn để khai thác toàn bộ tiềm năng của vật liệu bán dẫn đầy hứa hẹn này.**